A timing table defines the precise interface timing parameters required for stable LCD module operation, often having greater impact on system reliability than resolution specifications alone.

A timing table specifies the exact interface timing parameters an LCD module expects—pixel clock, horizontal/vertical active regions, total timing (active + porches + sync), porch lengths, sync pulse widths, and signal conventions. It can matter more than resolution because timing determines whether pixels are sampled reliably with margin across real operating conditions, while resolution only tells you how many pixels exist.

In LCD display module integration work at MEIDAYINGNUO, timing table mismatches1 often cause more field stability issues than resolution capability limits. Teams may focus on hitting a target resolution while treating timing as a secondary detail, and the result is an integration that looks fine on a bench but becomes unstable under temperature variation, cable routing constraints, or EMI exposure.

What is a timing table in an LCD module context?

A timing table defines the specific interface timing parameters required for proper LCD module operation and stable image display.

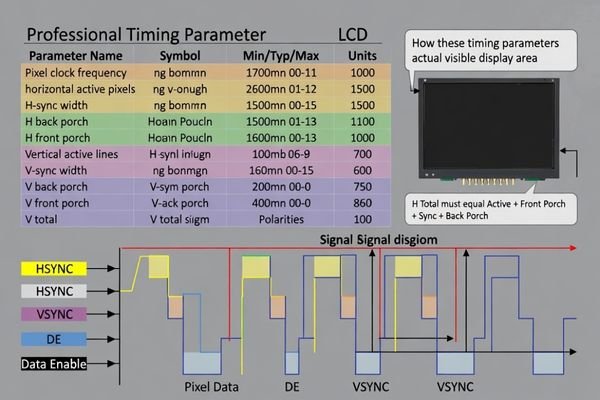

A timing table provides the explicit set of interface timing parameters that an LCD module expects for correct image data sampling, including pixel clock behavior, horizontal and vertical active regions, front and back porch requirements, sync pulse widths, and required signal polarities or conventions such as data enable versus sync-driven timing modes.

From an engineering standpoint, a timing table functions as the interface contract between the host controller and the LCD module. The same resolution can be delivered using different timing envelopes, but only the timing parameters2 that match the module’s expectations will produce stable images without flicker, tearing, intermittent blanking, or subtle artifacts that appear only in certain conditions. The fastest way to avoid bring-up guesswork is to treat the timing table as a first-class input and keep the host configuration aligned to it.

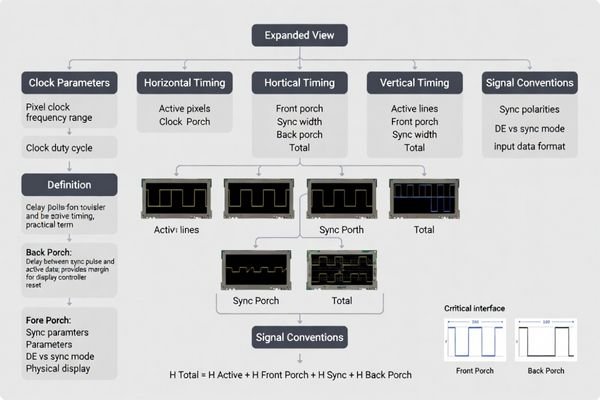

Timing Parameter Categories

Horizontal timing parameters define line structure including active pixel region, front porch, sync pulse width, and back porch requirements for proper line sampling and display synchronization.

Signal Convention Requirements

Interface signal conventions specify whether the module expects data enable control, horizontal/vertical sync signals, or specific polarity requirements for stable operation.

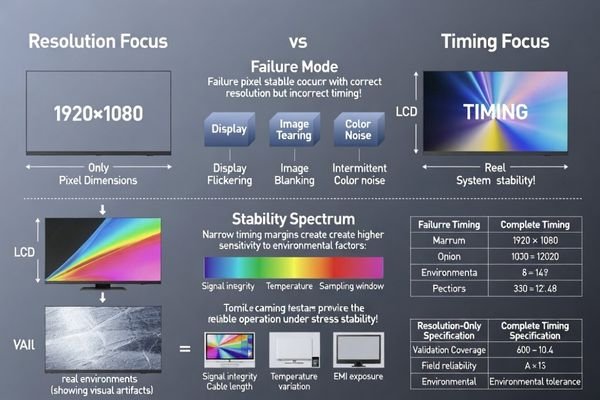

Why can timing matter more than resolution?

Timing parameters determine interface stability and reliability while resolution only defines pixel quantity, making timing critical for consistent operation.

Resolution specifies pixel quantity but timing determines whether pixels arrive when the panel can sample them correctly. Incorrect pixel clock, porch lengths, or sync relationships can cause intermittent instability, color noise, line jitter, or temperature-dependent failures even when the module displays an image, because timing affects the complete signal chain including cable behavior, EMI sensitivity, and power interactions.

Many field problems come from borderline timing implementations that work in lab conditions but fail under real-world stress. When timing margin is thin, normal variation—longer harnesses, different routing, temperature drift, or added electrical noise—can push the system over the edge and create behavior that looks random but is actually repeatable once you reproduce the stress conditions. The practical takeaway is to prioritize stable sampling margin3 over chasing higher resolution that forces aggressive clocks and tighter tolerances.

Which timing fields most often break bring-up if they are wrong?

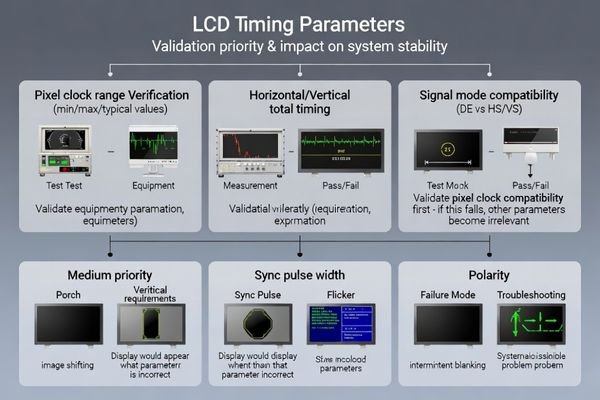

Specific timing parameters have disproportionate impact on bring-up success and system stability compared to other interface specifications.

The most critical timing failures involve pixel clock range mismatches, incorrect total line and frame timing calculations, and inconsistent sync or data enable signal assumptions. Pixel clock outside the module’s operating window causes unstable images and intermittent blanking, while wrong horizontal/vertical totals produce shifted images or prevent panel lock entirely.

Pixel clock compatibility is often the first hard constraint because it sets the fundamental sampling cadence. If the host cannot generate the required pixel clock within the module’s specified range with margin, you end up forced into compromises that surface later as intermittent failures. A reliable bring-up sequence is to lock down pixel clock, horizontal/vertical totals, and the expected signal mode (DE vs HS/VS) first, and only then tune secondary fields once the panel lock is stable.

| Timing Parameter | Failure Mode | System Impact | Validation Priority |

|---|---|---|---|

| Pixel Clock Range | Unstable sampling, intermittent blanking | Fundamental operation failure | Highest |

| Horizontal/Vertical Totals | Image shifting, lock failure | Display positioning errors | High |

| Signal Mode (DE vs HS/VS)4 | Unstable synchronization | Interface compatibility issues | High |

| Porch Requirements | Sampling window errors | Edge case stability problems | Medium |

Critical timing parameter validation prevents the most common integration failures while ensuring stable operation under stress conditions.

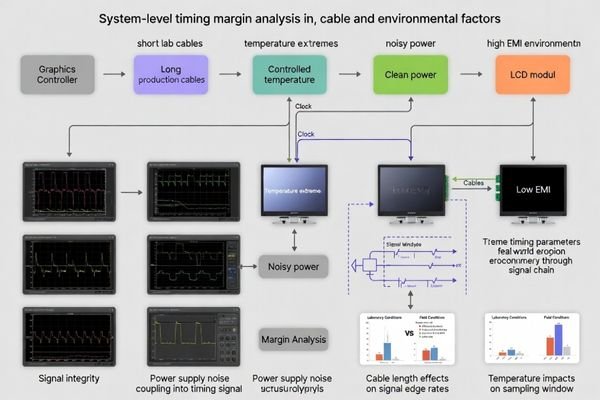

How do timing, interface margin, and signal integrity interact in real products?

Timing parameters interact with signal integrity and system margin to determine overall interface stability under real operating conditions.

Timing parameters affect the complete signal chain including controller margin, cable and connector behavior, EMI environment, and power system interactions. Timing configurations that work with short bench cables can become unstable with longer harnesses, noise exposure, or temperature drift because edge rates, jitter, and ground reference quality change the effective sampling window.

Aggressive pixel clock timing reduces system margin and increases sensitivity to reflections, crosstalk, and power supply noise, which can manifest as sparkles, line noise, or intermittent frame drops. These symptoms are frequently blamed on “module quality,” but they are often a sign that the timing configuration leaves too little room for real-world signal integrity variation. For timing margin analysis5 and signal chain optimization support during interface specification development, engineering teams can contact info@lcdmodulepro.com.

System-Level Margin Considerations

Interface timing must account for cable routing constraints, EMI environment, temperature variation, and power system behavior that affect signal quality and sampling window reliability.

Environmental Stress Impact

Real-world operating conditions including temperature cycling, mechanical vibration, and electrical noise exposure can degrade timing margin and require conservative timing parameter selection.

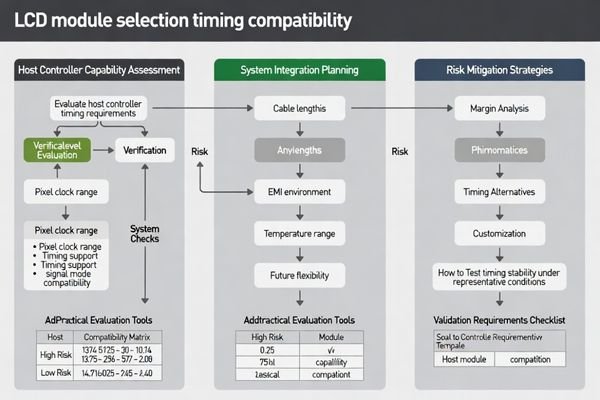

How do you use a timing table to de-risk an LCD module selection?

Systematic timing table evaluation during module selection prevents integration risks and ensures reliable operation across system variants and operating conditions.

Use timing tables as compatibility checklists between host controllers and modules by confirming pixel clock generation capability with margin, verifying horizontal/vertical timing support, and validating signal mode compatibility. Plan validation with representative cabling and enclosure conditions because timing that only works in laboratory setups is not production-ready.

Successful module selection requires early validation of timing compatibility6 under worst-case system conditions. If the design is likely to evolve (longer harness, tighter EMI environment, controller variant changes), prioritize timing configurations that keep comfortable margin rather than pushing the pixel clock or totals to their limits. If standard timing becomes risky due to host constraints, planning customization early can prevent late-stage redesign after mechanical and optical decisions have already locked the system into a narrow electrical corner.

Timing-Based Selection Workflow:

Host Controller Capability Assessment

- Verify pixel clock generation range with adequate margin

- Confirm horizontal/vertical total timing support

- Validate signal mode compatibility (DE vs HS/VS)

- Check porch requirement flexibility for future variants

System Integration Planning

- Evaluate timing margin with planned cable lengths

- Consider EMI environment impact on timing stability

- Plan validation under temperature and power variation

- Assess future flexibility for controller or harness changes

Risk Mitigation Strategies

- Prioritize timing configurations with comfortable margin

- Avoid pushing pixel clock to controller or module limits

- Plan alternative timing options for system variants

- Consider customization when standard timing creates risk

Validation Requirements

- Test with representative cable routing and enclosure

- Validate across temperature and power supply variation

- Confirm stability under EMI stress conditions

- Document working parameters for production reference

This approach treats timing compatibility as a primary selection criterion rather than a secondary integration detail, reducing field stability risks and avoiding late-stage redesign requirements.

FAQ

Is the timing table the same as resolution and refresh rate?

No. Resolution and refresh rate are outcomes, while the timing table defines the detailed horizontal/vertical totals, porches, sync widths, and signal conventions that produce those outcomes reliably.

Why does a panel show an image even when timing is wrong?

Many panels have some tolerance and may partially lock, but operating outside the intended window can cause intermittent instability, artifacts, or failures that appear only under stress (temperature, EMI, long cables).

What timing fields should I verify first during bring-up?

Pixel clock range, total horizontal/vertical timing, and the expected signal mode/polarities (DE vs HS/VS) are the top priorities because they most strongly affect lock stability.

How do timing issues differ from signal integrity problems?

Timing mismatches are usually deterministic (repeatable), while integrity problems often vary with cable movement, temperature, or EMI; in practice, borderline timing reduces margin and makes integrity issues more visible.

Can I "fix" timing problems with software post-processing?

Not reliably. Post-processing cannot correct sampling errors at the interface; the correct approach is to match the timing table and keep sufficient margin.

When should I consider customization related to timing?

When host capabilities, cabling constraints, or future variants make standard timing risky, aligning timing expectations early through customization can prevent late redesigns.

Conclusion

Timing tables function as interface contracts that determine LCD module stability and reliability beyond what resolution specifications alone can provide. Success requires treating timing parameters as primary selection criteria rather than secondary integration details, with systematic validation under representative system conditions including cable routing, EMI exposure, and temperature variation. Understanding the interaction between timing parameters and system-level margin enables better module selection decisions and prevents field stability problems that appear after production deployment.

MEIDAYINGNUO provides timing compatibility analysis and interface optimization support for LCD display module integration challenges. Our engineering team specializes in system-level timing validation that accounts for cable routing constraints, EMI environments, and operating condition variations to support stable long-term operation. Contact our technical team when timing compatibility analysis is critical for reliable LCD module integration and field performance validation.

✉️ info@lcdmodulepro.com

🌐 https://lcdmodulepro.com/

-

Understanding timing table mismatches can help prevent stability issues in LCD displays, ensuring better performance in real-world applications. ↩

-

Exploring timing parameters helps in grasping how to achieve optimal display performance and avoid common issues like flicker. ↩

-

Exploring stable sampling margin can help you enhance system reliability and performance in various applications. ↩

-

Exploring Signal Mode differences can help you grasp their impact on interface compatibility and synchronization stability. ↩

-

Understanding timing margin analysis is crucial for optimizing signal integrity and ensuring reliable system performance. ↩

-

Understanding timing compatibility is crucial for ensuring system stability and performance, especially in complex designs. ↩