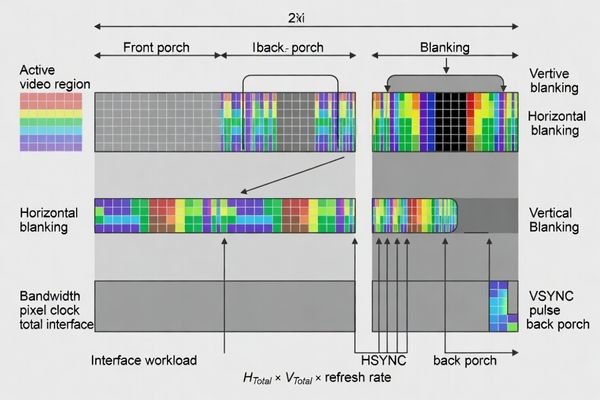

Blanking represents the non-active timing portions in display signals that consume interface bandwidth despite not carrying active image pixels, requiring careful consideration in system bandwidth calculations.

Blanking consists of horizontal and vertical timing intervals where the active video region is not present but interface timing continues, including front porches, sync pulses, and back porches that separate active display regions. While blanking appears "invisible," it consumes real interface bandwidth because timing generators still run through total pixels-per-line and total lines-per-frame (including blanking), making proper bandwidth budgeting essential for stable operation.

In my LCD display module integration work at MEIDAYINGNUO, I’ve found that blanking-related bandwidth miscalculations cause more late-stage integration problems than resolution capability issues. Teams often budget interface capacity based only on active pixel counts while overlooking the timing overhead1 that blanking intervals introduce, which can lead to flicker, intermittent frame drops, or temperature-dependent instability once real-world margins tighten.

What is blanking in a display timing signal?

Blanking defines the non-active timing portions of display signals that provide necessary timing structure without contributing visible image content.

Blanking includes horizontal blanking intervals between active pixel lines and vertical blanking periods between active display frames. These timing regions contain front porches, sync pulses, and back porches that coordinate line and frame boundaries, even though no active image pixels are presented during blanking periods.

From an engineering standpoint, I usually explain that blanking intervals represent mandatory timing overhead that affects total interface workload. The timing generator processes complete horizontal totals (active pixels plus blanking) multiplied by complete vertical totals (active lines plus blanking), so blanking remains a real bandwidth consumer even when the active video region is not present.

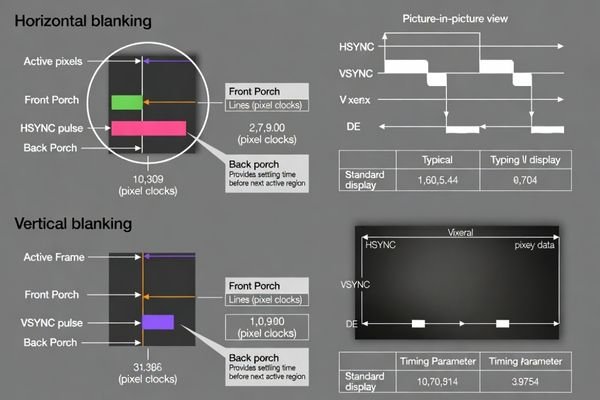

Horizontal Blanking Components2

Horizontal blanking includes front porch (after active pixels), sync pulse, and back porch (before next line’s active pixels) that provide line-to-line timing coordination and processing margin.

Vertical Blanking Structure

Vertical blanking contains front porch (after active frame), vertical sync, and back porch (before next frame) intervals that coordinate frame boundaries and accommodate panel refresh requirements.

Why does blanking exist if it doesn’t show anything?

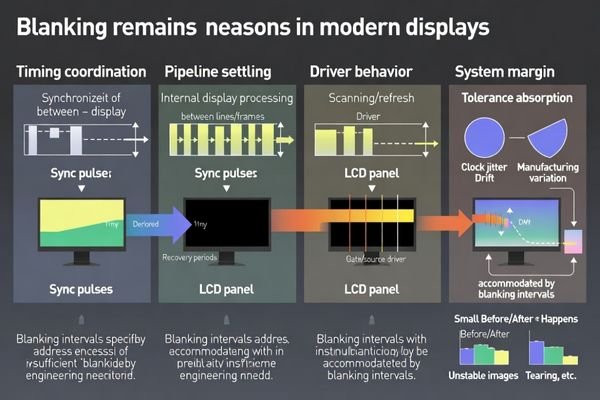

Blanking intervals provide essential timing coordination and system margin despite not contributing to visible image content.

Blanking persists in modern displays because it provides coordination windows between timing controllers and panels, accommodates internal pipeline settling requirements, aligns with panel driver behaviors, and offers engineering margin for clock tolerance, jitter, and manufacturing variations. Blanking intervals also absorb discrepancies between source output cadence and panel refresh requirements across operating conditions.

Based on the projects I support with timing optimization3, blanking intervals function as essential timing buffers that help maintain stable operation across temperature, voltage, and manufacturing variations. Systems that minimize blanking too aggressively may appear fine under ideal bench conditions but run into instability when clock drift, jitter, EMI exposure, or supply variation reduces timing and link margin.

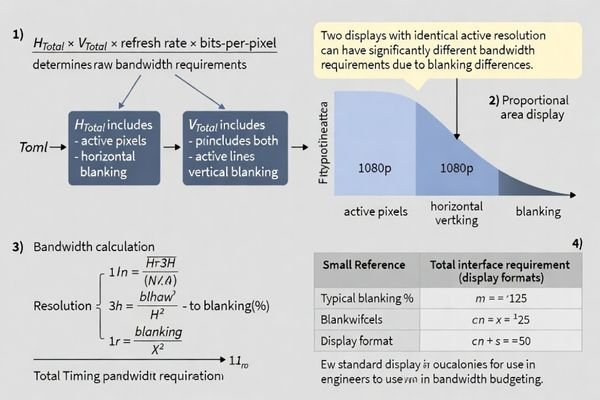

How does blanking change the bandwidth calculation?

Blanking intervals directly increase total timing requirements and interface bandwidth consumption beyond active pixel calculations.

Interface bandwidth must account for total transmitted timing including both active and blanking portions. A practical budgeting rule is: total timing workload scales with HTotal × VTotal × refresh rate (not HActive × VActive × refresh rate), and then you must apply the chosen interface’s efficiency and overhead. This means two modes with identical active resolution can require significantly different bandwidth if blanking totals differ.

When I troubleshoot bandwidth-related integration issues, teams often discover that nominal calculations based only on active pixels underestimate actual interface requirements. Safe bandwidth budgeting4 requires starting from complete timing parameters (HTotal, VTotal, refresh rate) and mapping through interface efficiency to verify sustainable data rates with margin; the breakdown below is a conceptual way to see how blanking contributes, but the final number should be calculated against your actual link/protocol overhead and lane utilization limits.

| Timing Component | Bandwidth Impact | Calculation Factor |

|---|---|---|

| Active Resolution | Visible pixel data | Width × Height × Refresh |

| Horizontal Blanking | Line timing overhead | (HTotal – HActive) × VTotal × Refresh |

| Vertical Blanking | Frame timing overhead | HTotal × (VTotal – VActive) × Refresh |

Complete bandwidth calculation requires summing active pixel data plus horizontal and vertical blanking overhead to determine total interface utilization.

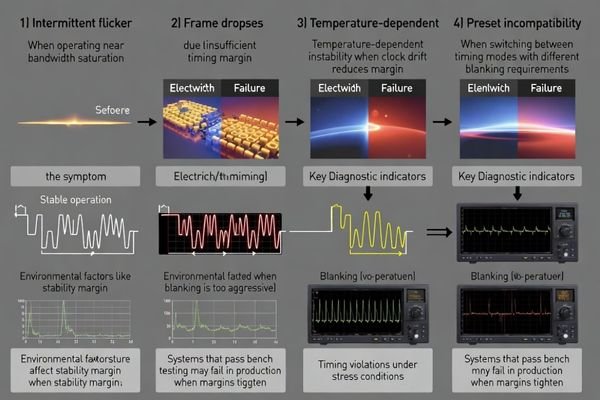

What practical pitfalls does blanking create in real designs?

Blanking-related bandwidth issues often manifest as margin problems that appear during production rather than initial development testing.

Common blanking pitfalls include intermittent flicker when links operate near saturation, unstable operation across temperature due to clock drift sensitivity, unexpected incompatibility when switching timing presets with different blanking totals, and assumptions that higher pixel clocks are always acceptable if active resolution remains unchanged while overlooking lane rate limits and protocol overhead.

I’ve observed that blanking problems typically present as "works on bench but fails in production" scenarios because designs pass nominal bandwidth checks yet become unstable when margins tighten under real operating conditions. These failures often correlate with temperature variation, harness or cable batch variation, grounding differences, backlight switching noise coupling, routing changes, or EMI exposure that degrades link quality. For comprehensive bandwidth analysis and timing validation support, engineering teams can contact info@lcdmodulepro.com during interface specification development.

Margin Erosion Effects

Insufficient bandwidth margin due to blanking miscalculation creates sensitivity to clock drift, jitter, and signal integrity degradation that manifests as intermittent display problems.

Temperature and Tolerance Sensitivity

Systems operating near bandwidth limits become unstable when component tolerances, clock accuracy, and signal quality vary across operating temperature ranges.

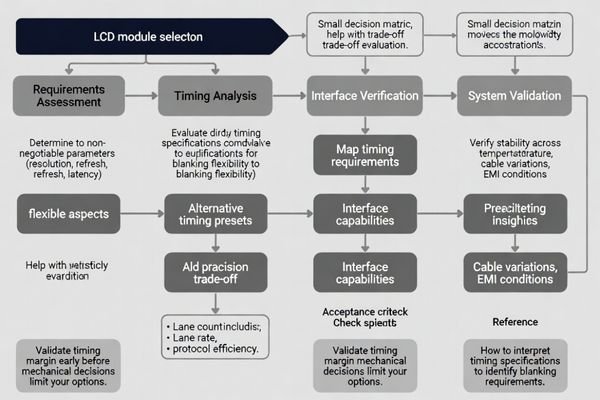

How to choose an LCD module when blanking pushes your bandwidth limits?

Strategic module selection requires balancing visible requirements against total timing workload and interface sustainability under real operating conditions.

When blanking inflates bandwidth requirements, optimize module selection by fixing non-negotiable parameters (visible resolution, target refresh, acceptable latency), examining timing flexibility within module acceptance ranges, and verifying end-to-end interface constraints including lane rates, encoding efficiency, and signal integrity budget across cable length and EMI environment.

Based on my experience with bandwidth-constrained integration projects, successful module selection requires early validation of timing compatibility5 under worst-case system conditions. Teams that prioritize optical or mechanical specifications without considering timing workload often discover bandwidth limitations during integration when correction options are expensive and time-consuming.

Bandwidth-Conscious Selection Approach

Assess fixed requirements first by stating the minimum visible resolution, refresh rate, and latency targets that you cannot compromise, then evaluate whether the module’s accepted timing windows allow safer totals (for example, alternative timing presets or tighter blanking where permitted) without pushing the link into saturation. Next, validate the entire interface chain—lane count and lane-rate ceilings, protocol overhead and efficiency, and the real signal-integrity budget across your PCB/FPC/cable and connector choices—under the EMI conditions and power/backlight noise profile your product will actually ship with. Finally, convert these checks into an integration output checklist: lock timing early, budget bandwidth from total timing plus overhead, verify link margin across temperature and supply variation, and confirm the mechanical/electrical design choices don’t erode margin during production scaling.

FAQ

Is blanking "wasted bandwidth," and can I always minimize it?

It’s not wasted in the sense of being optional; it is part of the required timing structure and often carries necessary margin for stability. Some systems allow reduced blanking, but it must remain within the LCD module’s timing acceptance and the source/link’s tolerance, otherwise you risk flicker, instability, or no display.

Why do two panels with the same resolution need different interface bandwidth?

Because their total timing (HTotal/VTotal) and accepted timing presets can differ, leading to different pixel clocks at the same refresh. Bandwidth must follow total timing plus link/protocol overhead, not just active pixels.

What symptoms suggest the link is failing due to tight blanking/bandwidth margin?

Typical symptoms include intermittent flicker, periodic frame drops, random black screens during temperature changes, or issues that appear only with specific timing presets. Problems that disappear when you reduce refresh or pixel clock often indicate a margin problem.

Does protocol overhead matter as much as blanking?

Yes. Blanking increases total timing workload, while protocol overhead reduces effective payload efficiency. Both stack together, so you should budget them simultaneously, especially when operating near lane-rate limits.

Can I solve bandwidth issues by just increasing the lane rate?

Sometimes, but lane-rate increases are constrained by the source, the LCD module’s interface capability, and signal integrity limits of your PCB/FPC/cable. Higher rates can also worsen EMI and reduce jitter margin, so it’s not always the safest fix.

When should I consider a custom LCD module because of blanking and bandwidth?

If your industrial design demands a special shape/aspect ratio, or your system is repeatedly forced into extreme pixel clocks to hit a UX target, customization can align the native resolution, timing acceptance, and mechanical constraints to regain margin and reliability.

Conclusion

Blanking represents unavoidable timing overhead that directly impacts interface bandwidth budgeting and system stability margin. Success requires treating blanking as a real bandwidth consumer rather than invisible overhead, calculating total timing workload including both active and blanking intervals, and validating interface capability under worst-case operating conditions. Understanding the relationship between blanking intervals and bandwidth consumption enables better module selection decisions and prevents late-stage integration failures that result from insufficient margin planning.

MEIDAYINGNUO can support bandwidth analysis and timing optimization for LCD module integration projects where blanking and real-world link overhead materially affect stability. Our engineering team focuses on system-level validation that accounts for blanking-driven timing totals, protocol efficiency, and signal integrity margins to help teams achieve stable operation across operating conditions and production variation. Contact our technical team when blanking and bandwidth constraints require deeper interface margin analysis and long-term stability validation.

✉️ info@lcdmodulepro.com

🌐 https://lcdmodulepro.com/

-

Exploring timing overhead will provide insights into optimizing interface capacity and enhancing display stability. ↩

-

Exploring horizontal blanking components helps in grasping the timing coordination essential for video signal processing. ↩

-

Exploring timing optimization techniques can enhance your knowledge and improve system reliability. ↩

-

Understanding bandwidth budgeting is crucial for ensuring efficient data transfer and avoiding integration issues. ↩

-

Understanding timing compatibility is crucial for successful integration, ensuring that all components work harmoniously under worst-case conditions. ↩