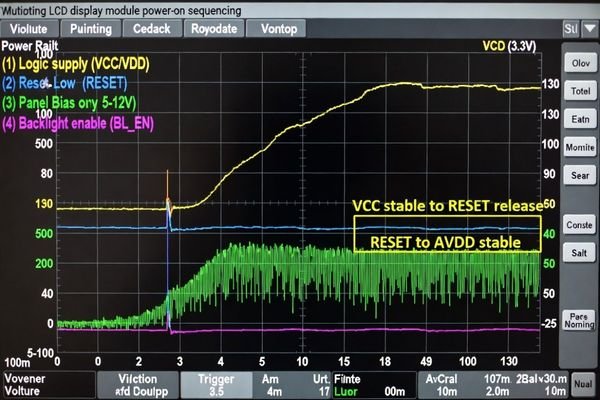

Power-on sequencing validation is how I de-risk “random” display bring-up issues before they become field returns. The goal isn’t a single successful boot—it’s repeatable, deterministic startup across the messy power conditions a real product sees.

Power-on sequencing is the contract defining the precise order, timing, and voltage characteristics for applying power and control signals to an LCD module. It must be strictly validated with a repeatable setup that mimics the final product’s electrical environment, including stress cases like fast power cycling and brownouts, to prevent intermittent boot failures, image artifacts, and long-term reliability issues.

In my LCD display module integration work at LCD Module Pro, the “worst” sequencing bugs are the ones that only show up once every 50 boots. On a clean bench supply with short leads, everything looks fine; in the product with real harness resistance, shared grounds, and inrush, margins disappear.

That’s why I treat sequencing validation like a mini qualification effort: define the sequencing contract, measure at the module connector (not just at regulators), and then prove repeatability under stress loops1. If you can’t make it fail in the lab, you’ll meet it in production.

What does “power-on sequencing” mean for an LCD display module, and why is it so strict?

Power-on sequencing isn’t just “turn power on”—it’s a specific startup recipe the module needs to enter a known state. If the module’s internal controller boots half-awake, you can get a blank screen, a quick flash, or a “works only after reset” situation that’s brutal to debug.

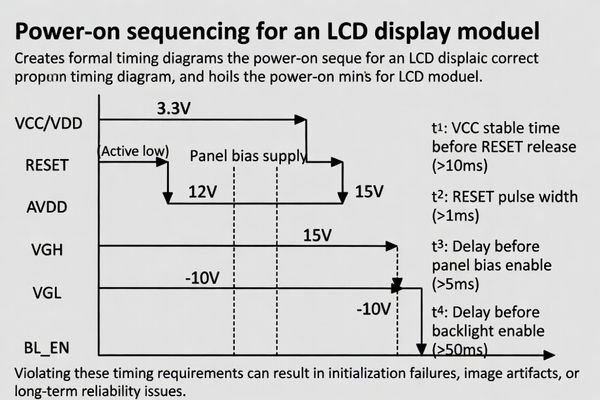

Power-on sequencing is the agreed order and timing window for bringing up logic power, panel bias rails, reset, and backlight so the module’s controller and panel drivers enter a defined state every time. It’s strict because state machines and analog bias conditions can latch incorrect states if rails ramp in the wrong order or reset releases too early, causing intermittent blank screens, flicker, artifacts, or stress.

I usually explain it like this: the module has multiple subsystems that “wake up” at different speeds. If one subsystem starts talking before another is stable, you create a race condition. The tricky part is that a race condition2 can look perfect 99% of the time.

The Internal State Machine

Inside the module, controller logic and driver ICs rely on a clean reset and stable logic power to start predictably. If reset de-asserts while logic power is still ramping or bouncing, the controller can land in an undefined state that only a full power cycle clears.

Beyond Simple Delays

Delays matter, but so do ramp quality and thresholds. A rail that rises and dips (“non-monotonic ramp”) can be interpreted as an on/off event, and a rail that looks stable at the regulator can still droop at the module connector due to IR drop and ground bounce during inrush.

Which rails and control signals usually define the sequencing contract?

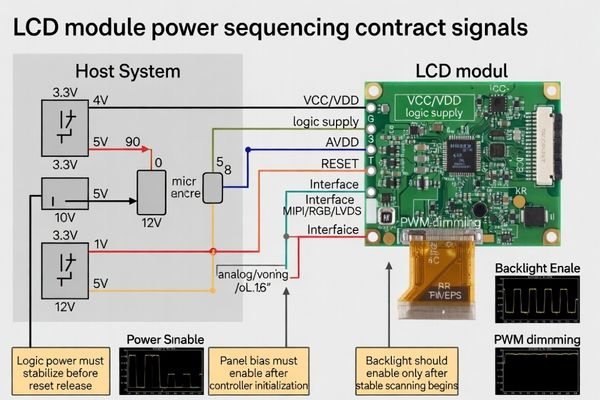

A sequencing contract is basically: “Which signals can change the module’s internal state, and in what order are they allowed to move?” If you don’t write this down explicitly, teams end up guessing with fixed delays—and that’s where intermittent failures live.

A robust sequencing contract names every rail and control line that can change the module’s internal state: logic supply, analog/bias supplies for panel driving, reset, interface enable/clocking readiness, and backlight enable/dimming. Validation starts by mapping your host power tree to the module’s expected order, then identifying the must-be-stable-before relationships and measuring at the module input, where droop and bounce actually occur.

When I kick off a sequencing review, I draw a simple timing diagram and annotate “stable” with a voltage tolerance and a minimum time. “Looks good” is not a spec—stable needs a threshold.

| Signal / Rail | Purpose | Typical Sequencing Rule |

|---|---|---|

| Logic Supply (VCC/VDD) | Powers the module’s digital controller and timing logic. | Must be the first rail to come up and stabilize within its specified tolerance. |

| Panel Bias Rails (AVDD, VGH, VGL) | Provide the analog voltages needed to drive the TFT backplane. | Must only be enabled after the logic supply is stable3 and the reset is released. |

| Reset (RESET/RST) | Holds the module’s controller in a known state. | Must be held low until the logic supply is stable, then released with a clean rising edge. |

| Backlight Enable (BL_EN/PWM) | Controls the backlight power supply. | Must only be enabled after stable scanning to avoid startup artifacts and stress. |

One important note: rail names and “who generates what” vary by module design. The table is a template—your contract should match the module datasheet and the actual system power tree.

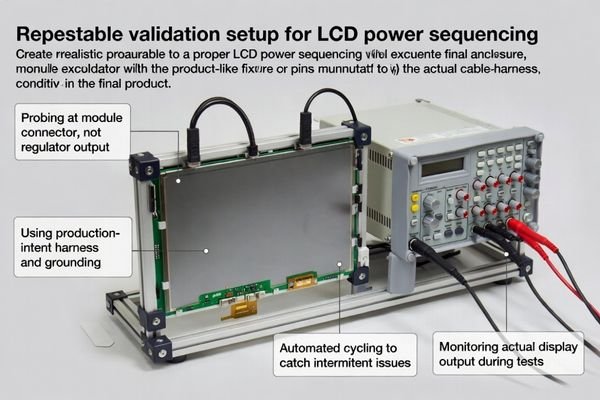

How do you design a repeatable validation setup that won’t hide sequencing faults?

The fastest way to “validate” a bad sequence is to accidentally make the lab setup nicer than the product. I’ve seen teams fix nothing because the bench supply and short leads quietly cover up real droop and reset glitches.

A repeatable validation setup uses final-intent harness length, grounding, and power source behavior, and measures rails and control signals at the module connector. It should log multiple cycles with consistent triggers (power button, main enable, reset release) and avoid masking faults with oversized lab supplies or unrealistic cabling that eliminates droop and ramp imperfections.

If you only take one thing from this section: probe at the module input pins with good probing technique4. Measuring at the regulator output is useful, but it’s not the voltage the module actually sees during inrush and transitions.

I also like to keep the setup “production honest”: the real adapter, the real harness, the real enclosure grounding. If your validation requires a lab supply and a short cable to pass, that’s a warning sign.

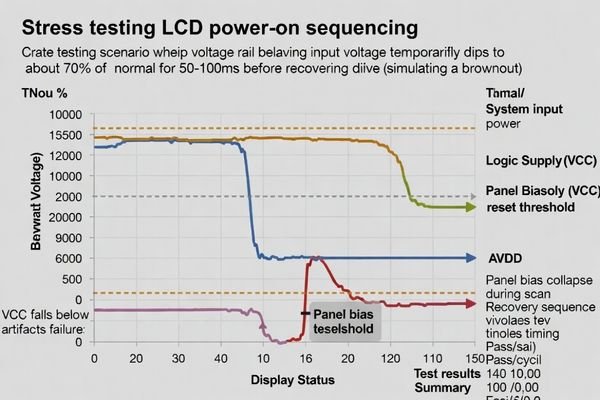

What stress cases prove your sequencing works beyond a single cold boot?

A single cold boot at room temperature is the easiest test you’ll ever pass. The real proof is whether the module comes up cleanly when you abuse the sequence in the same ways real users and real power systems do.

Robust validation must include stress loops and corner cases: fast power cycling, repeated reset toggling, sleep/wake transitions, and brownout recovery where rails dip and return. Add temperature and supply tolerance because ramp rates and timing windows shift across corners. Pass/fail should include stable image, no artifacts, no stuck states, and consistent bring-up time distribution across many cycles.

Here’s my “minimum meaningful” set: cold boot loops5, fast off/on cycles, sleep/resume loops, and at least one controlled brownout profile. These are the scenarios that expose race conditions and marginal thresholds.

Dynamic Stress Cases

Automate repeated cycles so you can see the failure rate, not just “it failed once.” Fast power cycling is especially revealing because rails may start from a partially charged state and reset timing shifts relative to rail thresholds.

Corner Condition Testing

Run the same stress loops at temperature extremes and at minimum/maximum input voltage. Regulators, supervisors, and oscillators behave differently at corners, and sequencing margins that look generous at 25°C can shrink quickly.

How to choose an LCD module with power-on sequencing constraints in mind?

If your host platform has limited rail control, a module with a very tight multi-rail sequence can become a hidden integration risk. I try to select modules where the host can meet the contract with margin, not with “perfect timing.”

When I’m helping a client pick a module, I treat sequencing requirements like part of the interface. If the host can’t control rails cleanly or can’t guarantee reset timing, you’ll end up compensating later with hacks.

Host capability fit

First, I check how many independent rails the platform can control and how reset is generated (supervisor vs RC). If you can’t hold reset low until VCC is truly stable at the module connector, you’ll fight intermittent boots.

Prefer margin and simpler power trees

When possible, I prefer modules that generate more internal rails themselves from a single input, or at least tolerate wider timing windows. A simpler external sequencing contract is usually easier to validate and more resilient in production.

FAQ

Why does a module work on the bench but fail after integration into the product?

Bench setups often have shorter wiring, stronger supplies, and cleaner grounding, which can hide droop, ramp non-monotonicity, and reset glitches that appear in the real harness and enclosure.

Is power-on sequencing only about adding fixed delays?

No. It also includes ramp slope, monotonicity, stable thresholds, rail dependencies, reset pulse shape, and behavior during fast cycling and brownouts.

Should backlight be enabled as soon as the module powers up?

Usually not. Enabling backlight before stable scanning can expose artifacts and add stress; it’s safer to gate backlight after the panel is confirmed in a stable display state.

What measurements matter most during sequencing validation?

Measure at the module input: key rails, reset, enable lines, and any rail-good signals, with consistent triggering and multiple-cycle logging to catch intermittent edge cases.

How do brownouts create hard-to-debug display issues?

Partial rail dips can leave controllers in undefined states where they don’t fully reset, causing intermittent blanking or artifacts until a full power cycle restores a clean start.

How do you prevent sequencing regressions after supplier revisions?

Freeze the validated configuration and require change notification; re-run the key sequencing stress loops (cold boot, fast cycle, sleep/wake, brownout) on new revisions.

Conclusion

Validating power-on sequencing requirements for an LCD display module is about proving repeatability, not just achieving a single successful startup. The practical recipe is: define the sequencing contract, measure at the module connector, and then run stress loops (fast cycling, sleep/wake, brownouts) across corners so you catch race conditions before production does.

At LCD Module Pro, I treat sequencing as part of the system integration contract, because it directly affects bring-up stability, artifacts, and long-term reliability. If you’re seeing intermittent boots or hard-to-reproduce flicker during startup, our engineering team can help you turn it into a measurable test plan and close the margin gaps early.

✉️ info@lcdmodulepro.com

🌐 https://lcdmodulepro.com/

-

Exploring the impact of stress loops can help you identify potential failure points and improve the robustness of your designs. ↩

-

Understanding race conditions is crucial for designing reliable systems. This resource will deepen your knowledge on the topic. ↩

-

Understanding the definition of ‘stable’ in power sequencing is crucial for ensuring reliable operation of electronic modules. ↩

-

Understanding good probing techniques is essential for accurate measurements in electronics, ensuring reliable performance. ↩

-

Understanding cold boot loops can help you identify and mitigate system failures effectively. ↩