When developing a device that needs to support multiple display resolutions, engineers often face a frustrating problem: the LCD display module works perfectly at its native resolution but shows artifacts—shifted geometry, cropped edges, flicker, or banding—immediately after switching to a different mode. When the issue is mode-specific and repeatable, timing mismatch is often the real root cause.

Diagnosing artifacts after a resolution change starts by identifying repeatable, geometric patterns that indicate a timing-parameter mismatch (totals, porches/blanking, sync widths, sync polarity, pixel clock). The key is to verify the host’s full timing tuple for the target mode matches the LCD module/TCON expectations, not just the active resolution.

In LCD Module Pro customer integrations, teams often assume a noisy signal or a defective panel is to blame. However, many “after-switch” artifacts come from a mismatch between what the host timing generator1 outputs and what the module timing controller (TCON) expects for that mode. The panel isn’t broken—it is being framed incorrectly.

This is especially common when a scaler or a complex SoC generates non-native modes. Those platforms can introduce rounding, clamp porch values, or switch clocking behavior during mode changes. The result can be a clean signal electrically, but with totals/blanking that cause the receiver to sample or frame lines incorrectly. The workflow below makes the problem repeatable, measurable, and fixable.

What artifact patterns indicate a timing-parameter mismatch after a resolution change?

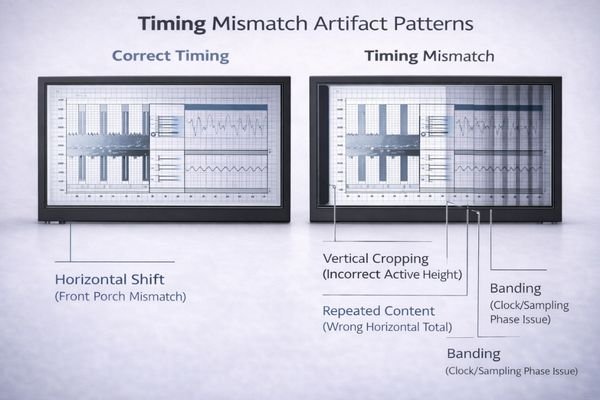

The first step in any diagnosis is to carefully observe the artifact. Unlike random EMI noise, timing-related artifacts are typically stable, repeatable, and aligned to the pixel grid.

Timing-mismatch artifacts are usually repeatable and geometric: shifted images, cropped edges, repeated columns/rows, stable vertical banding, or mode-specific “sparkle.” A strong clue is that the issue appears only in a specific non-native mode and disappears when returning to the module’s native timing.

A useful triage step is to classify what you see: is it a framing/geometry error (active area and blanking boundaries) or a lock/stability error (sync/clock acceptance)? That choice determines which timing knobs you should touch first.

Geometric and Positional Artifacts

These are common timing-mismatch signatures. They occur when the host and the module disagree on where the active video begins/ends within the total frame.

- Shifted Image: The picture is offset horizontally or vertically, often leaving bars on one side. This strongly implicates front/back porch values.

- Cropped Edges: Content is missing at one or more edges. This can result from incorrect active width/height or an active window that does not align with the receiver’s framing.

- Repeated Columns or Rows: A region duplicates or “wraps.” This is often caused by incorrect total horizontal/vertical counts that make the receiver restart a line or frame at the wrong time.

Stability and Lock-Related Artifacts

These suggest the receiver is struggling to lock or sample consistently after the mode switch.

- Vertical Banding or “Sparkle”: Regular stripes or flickering pixels can come from totals/pixel clock combinations that create sampling phase issues at the receiver.

- Intermittent Blackouts or Rolling: Brief loss of sync suggests sync width/polarity or clock acceptance constraints are violated in that mode.

If the artifact is identical every time you switch to that mode, treat timing as the primary suspect until proven otherwise.

Which timing parameters are most likely to be wrong when switching modes?

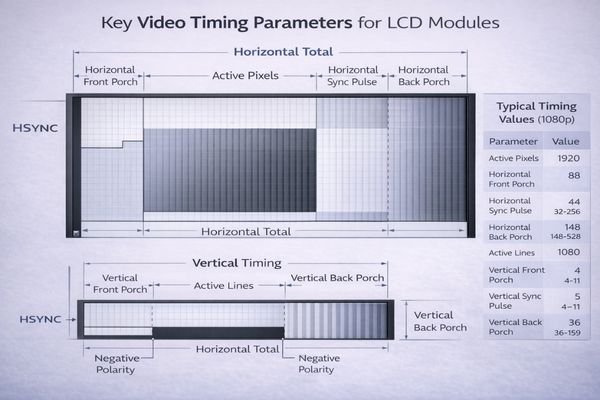

When artifacts appear after a resolution change, the issue is rarely the “resolution” itself (e.g., 1280×800). The issue is usually the detailed timing set that defines the frame structure—your timing tuple.

The most error-prone parameters are the frame-structure values: horizontal/vertical totals, active width/height, front/back porch values, sync pulse widths, and HSYNC/VSYNC polarity. If these do not match what the module expects for that mode, the host and TCON disagree on line/frame boundaries and sampling behavior.

Debugging should begin with an audit of the full tuple, not a quick check of active pixels. Common culprits include:

- Total Horizontal/Vertical Pixels: Totals define the full line/frame period. Incorrect totals can create stable banding, repeated regions, or unstable acceptance even if active pixels are correct.

- Front Porch, Back Porch, and Sync Pulse Width: Blanking positions the active image inside the frame. Wrong porch values commonly cause shifts and can also reduce receiver margin at the mode switch.

- Sync Polarity (HSYNC/VSYNC): Some TCONs are polarity-sensitive. A mismatch can cause intermittent lock, flicker, or loss of image after switching.

- Pixel Clock Frequency/Generation: Even when the nominal frequency is correct, mode switching can change the clock source, dividers, or PLL state. Combined with marginal totals/blanking, this can trigger artifacts only after reconfiguration.

If a scaler or bridge is in the path, add two more risks: timing rounding/clamping and hidden re-timing that overrides what the host “thinks” it is outputting.

How do you isolate timing issues from signal integrity, cable, or EMI problems?

A common diagnostic challenge is distinguishing between a timing mismatch and physical-layer issues like marginal signal integrity, a bad cable, or EMI.

Use controlled A/B testing. If changing only timing parameters (porches, totals, polarity) moves or fixes the artifact, it’s timing. If artifacts remain unchanged across multiple known-good timing sets and worsen with higher pixel clock, longer cables, or noisy environments, suspect signal integrity or EMI.

A practical isolation workflow:

- Test a Known-Good Mode: Switch back to the module’s native mode using datasheet-recommended timing. If artifacts vanish, your non-native mode timing is the primary suspect.

- Make Small, Controlled Timing Changes: Adjust one knob at a time (e.g., add a small horizontal front porch increment). If the image shifts by the same amount, you have confirmed a timing/framing issue.

- Vary the Physical Setup: Use a short, high-quality cable and minimal routing. If artifacts disappear only with a “better” physical setup, you likely have SI/EMI margin limits that are being exposed by higher clock stress.

- Observe Grid Alignment: Timing artifacts are usually pixel-grid aligned and repeatable. EMI artifacts tend to be more sporadic and less geometrically consistent.

A fast confirmation step is to apply a vendor-provided known-good timing table for the problematic mode (when available). If that clears artifacts, your custom timing generation or mode table is the likely root cause.

What step-by-step measurements and tests confirm the correct timing tuple?

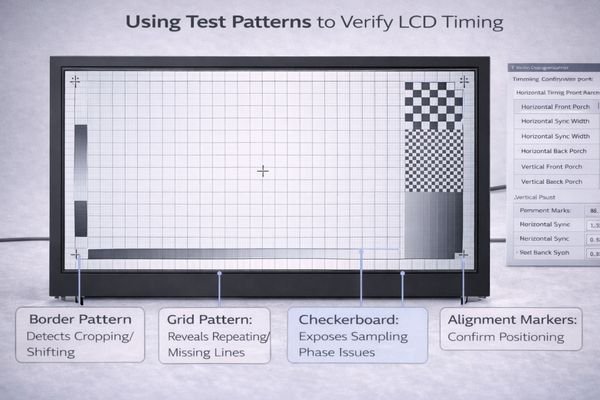

Once you suspect timing, the fastest path is to capture what the system is actually outputting, compare it to constraints, and then use minimal perturbations plus test patterns to confirm control.

Confirm the timing tuple by reading the host’s actual output parameters (clock, totals, porches, sync widths, polarity), comparing them to module constraints, then using diagnostic patterns and small perturbation sweeps to observe predictable artifact changes before locking the final timing set.

A reliable step-by-step process:

- Read the Registers: Verify the real pixel clock, totals, porches, sync widths, and polarities the host is outputting after the mode switch (don’t assume your programmed values survived).

- Compare with the Datasheet/Constraints: Build a simple comparison table and check minimum/maximum limits for blanking and sync widths.

- Use Diagnostic Test Patterns: A 1-pixel border exposes shift/crop immediately. Grids and fine checkerboards expose repetition and banding.

- Perform a Perturbation Sweep: Change one parameter in small increments (e.g., adjust horizontal front porch). If the symptom moves predictably, you’ve identified which framing element is wrong.

- Validate Stability: Repeat cold boots, warm reboots, and repeated resolution toggles. Borderline timing can “work once” but fail after state transitions.

If a bridge/scaler exists, confirm it is not silently re-scaling or re-timing during the switch, and confirm the output at the module connector, not only at the host side.

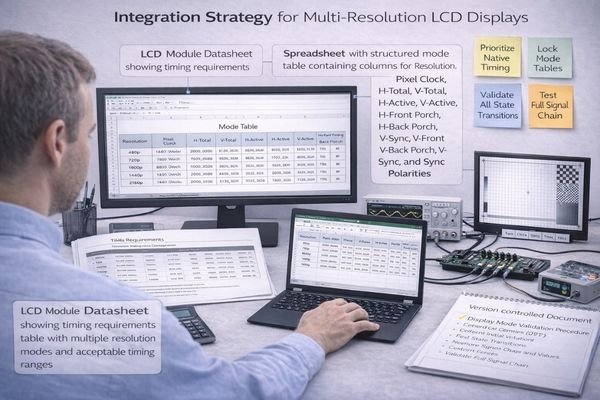

How should you select an LCD display module and integration strategy to reduce resolution-switch artifact risk?

The best way to solve resolution-switch artifacts is to prevent fragile timing modes from entering the product in the first place by minimizing custom modes and controlling mode tables as configuration items.

Reduce risk by prioritizing the module’s native timing, selecting modules with clear timing constraints, and using a locked, validated mode table for every supported resolution. Ensure the host/scaler can generate stable clocks without rounding surprises, and validate modes on the real signal chain (cable, connectors, bridge) across temperature and state transitions.

A practical strategy that holds up in production:

- Prioritize Native Timing: Use the module’s native mode as the default and treat non-native modes as exceptions that require explicit validation.

- Choose Well-Documented Modules: Prefer suppliers that provide clear timing tables and acceptable ranges for totals/blanking/sync and polarity requirements.

- Validate the Entire Signal Chain: Validate with the production harness, connectors, and any bridge/scaler, not only with a short lab cable.

- Create a Fixed Mode Table: Define a limited, controlled set of modes and lock exact parameters. Avoid generating timing “on the fly” unless the platform explicitly supports robust negotiation.

- Version and Re-Verify Timing: Treat timing tables like firmware configuration—version them and re-test after platform firmware updates or supplier changes.

FAQ

Why do artifacts appear only after switching resolution, not at cold boot?

Mode switching can change clock generation, scaler behavior, or receiver state; a borderline timing set may work at boot but fail after reconfiguration or state transitions.

Can wrong blanking values cause vertical stripes or repeated columns?

Yes. If totals and porches don’t match the receiver’s expected line framing, pixels can be sampled with the wrong alignment, creating repeat patterns or banding.

If lowering pixel clock helps, is it always a timing issue?

Not always; it can also improve signal integrity margin. Use controlled timing changes and mode comparisons to separate SI margin issues from pure parameter mismatch.

Should I rely on EDID-like auto-detection for embedded modules?

Many embedded modules use fixed timing expectations; relying on auto-detection can be risky unless your platform and module explicitly support a robust negotiation mechanism.

What’s the quickest confirmation that my timing table is wrong?

Switching to a vendor-provided known-good timing mode that eliminates artifacts strongly indicates your custom timing generation or parameters are incorrect.

When is customization preferable for multi-resolution support?

If you need unusual modes, tight EMI constraints, or long harnesses, tailoring the integration (signal chain and validated mode tables) can reduce risk versus ad-hoc tuning.

Conclusion

When an LCD display module shows artifacts after a resolution change, the cause is often a mismatch in the timing tuple rather than a hardware defect. The fastest diagnostic path is to classify the artifact, verify what timing is actually being output after the switch, and use minimal perturbation tests with clear patterns to confirm which parameter controls the symptom. Once a stable timing set is found, it must be validated across cold boots, warm reboots, and repeated mode toggles to prevent “works once” failures.

At LCD Module Pro, we support multi-resolution integrations by aligning module timing requirements with host generation behavior, validating on the real signal chain, and helping teams lock deterministic mode tables that resist regression across revisions and updates.

✉️ info@lcdmodulepro.com

🌐 https://lcdmodulepro.com/

-

Understanding timing generators is crucial for diagnosing and fixing display issues effectively. ↩