When selecting an LCD display module for a high-resolution application, the interface specification is one of the most critical parameters. Terms like "4CH LVDS" are common, but misunderstanding them can lead to host incompatibility, bring-up failures, and costly schedule slips—often showing up as partial images, repeating bands, or a stable but corrupted picture.

4CH LVDS is a four-channel parallel LVDS transport used to carry one image stream with higher pixel throughput and better per-channel signal margin. It is a hard interface requirement (not redundancy), so success depends on matching host capability, channel mapping, timing, and synchronized harness design—while treating resolution as a hint and confirming the required channel definition in the module documentation.

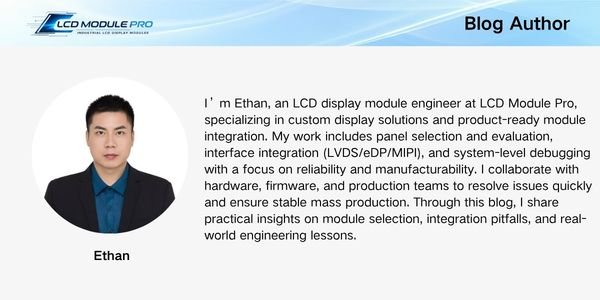

In LCD Module Pro customer integrations, LVDS is often assumed to be plug-and-play. In reality, the channel count—single, dual, or quad—defines the interface bandwidth and the physical/electrical requirements. "4CH LVDS" is not an optional feature; it dictates host output capability, connector pinout, cable routing, and validation needs.

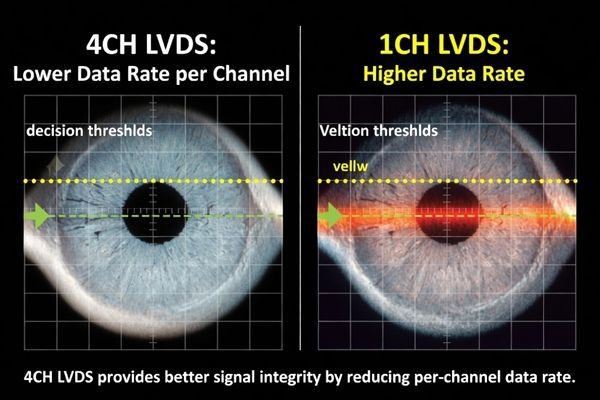

Multi-channel LVDS exists because pushing a single link to extreme data rates reduces eye margin and makes real products sensitive to harness length, connector discontinuities, and EMI. Splitting the pixel stream across four synchronized channels lowers the per-channel rate for the same payload and improves robustness. This article explains what 4CH LVDS1 means, why it’s used, and how to integrate it reliably.

What does “4CH LVDS” mean in an LCD display module?

Understanding the definition of 4CH LVDS is the first step toward a successful integration.

In an LCD module, "4CH LVDS" means pixel data for one image is split and transmitted over four synchronized LVDS channels in parallel. It is a bandwidth extension method, not redundancy, and it requires a host platform that can output true 4-channel LVDS with the correct mapping and timing.

Channel count is non-negotiable: a host designed for dual-channel LVDS cannot reliably drive a 4CH LVDS module unless an explicit bridge/conversion solution is validated.

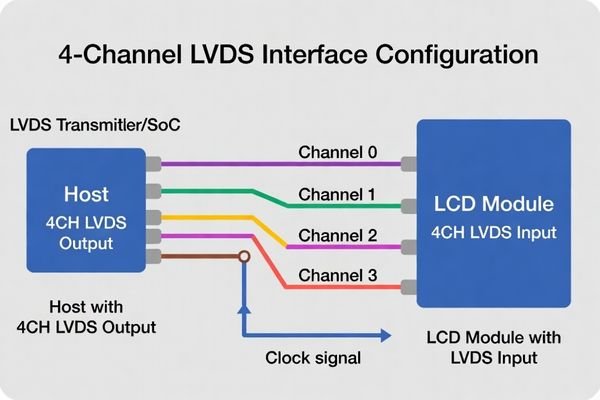

A Parallel Transport for Bandwidth

Think of 4CH LVDS as four parallel lanes carrying one image stream. Instead of forcing one or two lanes to run at very high rate, the system divides the payload and transmits it over four channels in lockstep. This reduces the per-channel data rate and improves tolerance to real harness effects such as loss, skew, connector reflections, and EMI.

Not Redundancy, but a Hard Requirement

The four channels are not backups. The module’s timing controller (TCON)2 expects all channels to be present and aligned to reconstruct the complete frame. If one channel is missing or mis-mapped, the result is typically a non-functional state: missing sections, repeated bands, quarter/partial images, or a stable but scrambled picture. Treat 4CH LVDS as a fixed interface definition that must match the host and cable design exactly.

Why do some panels need 4CH LVDS instead of single or dual LVDS?

4CH LVDS is adopted when the required pixel throughput pushes single/dual LVDS too close to physical margins for reliable operation.

Panels use 4CH LVDS when pixel throughput (resolution × refresh × color depth plus timing overhead) exceeds what single or dual LVDS can carry with sufficient margin. Splitting across four channels lowers per-channel rate, widens eye margin, and improves robustness across long cables, skew, crosstalk, temperature, and EMI stress.

Intermittent artifacts3 that appear only with longer harnesses or in noisy cabinets are often margin problems, not “bad panels.” As pixel clock increases, LVDS serialization rates rise and systems become more sensitive to loss, pair-to-pair skew, and crosstalk. 4CH LVDS reduces per-channel stress for the same payload, which is why it is common in industrial and commercial products where harnesses are longer and noise is higher than in lab setups.

Which resolutions and use cases commonly drive 4CH LVDS adoption?

There is no single resolution that universally requires 4CH LVDS. The driver is pixel throughput and the margin required by the product environment.

4CH LVDS commonly appears in higher-throughput display modes used for dense UI content on larger panels—especially where long harnesses or EMI reduce link margin. While “which resolutions use it” varies by panel ecosystem and timing constraints, 4CH tends to show up as designs move beyond mainstream HD-class timings into higher pixel payloads (higher resolution, higher refresh, or higher color depth). Always confirm the required channel definition and timing in the module datasheet.

A practical way to interpret “commonly used resolutions” is to treat resolution as a flag that you may be entering a higher-throughput regime. The decision is usually driven by one or more of these factors:

| Factor | Why It Drives 4CH LVDS Adoption | Example Use Cases |

|---|---|---|

| Higher pixel throughput4 | More pixels per second pushes single/dual LVDS toward tight margin. | Industrial operator stations with dense UI, transportation information terminals, large kiosk UI layouts. |

| Higher refresh and/or color depth | Higher refresh or deeper color increases payload per second. | Motion-heavy UI, high-fidelity UI stacks where smooth gradients matter. |

| Long cable runs | Loss and skew increase with harness length; lower per-channel rate improves robustness. | Remote display placements, long internal harness routing in cabinets. |

| Noisy EMI environments | Wider eye margin helps resist interference from motors, supplies, and RF subsystems. | Factory automation HMIs, self-service devices with motors and payment/RF modules. |

Best practice: use this table to understand why 4CH might appear, then confirm channel count, mapping, and timing from the module’s official interface definition.

How do you verify host compatibility and avoid 4CH LVDS integration failures?

4CH LVDS failures most often come from assuming “LVDS is LVDS,” misconfiguring mapping, or under-designing the harness as if channels are independent.

Avoid failures by confirming the host supports true 4-channel LVDS output with the required mapping, locking the full timing tuple, and treating the harness as one synchronized bus with length matching, controlled impedance, and solid return paths. Verify all channels toggle at the module connector using diagnostic patterns, then validate across temperature and worst-noise conditions.

Successful integration requires discipline in configuration and physical layer design.

Confirm Host Capability and Configuration

Verify in the host SoC/FPGA documentation that four synchronized LVDS channels5 are supported. Then confirm the required mapping format and lane/channel assignment expected by the module. Lock the timing tuple (pixel clock, totals, porches, sync widths/polarity) and ensure your mode generator does not silently clamp or round values during bring-up or mode switching.

Design a Synchronized Interconnect

Treat four channels as one bus: keep channel-to-channel length and skew closely matched, maintain controlled differential impedance, and preserve consistent return paths. Poor return paths can increase common-mode conversion and EMI, and unequal channel delays can corrupt reconstruction at the TCON. In bring-up, confirm activity on all channels at the module connector and use patterns that reveal split/mapping errors (repeat bands, missing columns, partial images).

How should you shortlist LCD display modules when 4CH LVDS is required?

For 4CH LVDS, shortlisting should focus on integration margin and lifecycle risk—not only size and resolution.

When shortlisting 4CH LVDS modules, prioritize documentation clarity (mapping/timing/pinout), verify host compatibility, assess the full signal chain (harness length, skew, EMI, grounding), and validate power/thermal behavior in the real enclosure. Also require strong change control because 4CH replacements are rarely drop-in.

Rather than treating the module as interchangeable, evaluate it as part of a complete signal-and-power chain:

- Documentation and support: Clear mapping/timing definitions, connector pinout clarity, and responsive integration support.

- Signal chain risk: Connector robustness, harness routing complexity, channel length-matching feasibility, and EMI environment.

- Power and thermal behavior: Brightness targets without unstable rails, and sufficient thermal margin in the enclosure.

- Lifecycle and change control: Clear PCN and EOL early-warning alignment so interface definitions don’t change silently and force redesign late.

FAQ

Is 4CH LVDS the same as “quad-link” LVDS, and is it backward compatible?

It generally means four parallel LVDS channels for one image stream and is not backward compatible with single/dual output unless the module explicitly supports multiple modes.

Will a 4CH panel display “something” if only two channels are connected?

Some systems may show partial or corrupted content, but reliable operation requires all channels with correct mapping and timing.

Do 4CH LVDS systems have higher EMI risk?

They can if return paths and harness design are poor; good impedance control, length matching, and grounding practices can keep EMI manageable.

What’s the fastest bring-up check for a suspected 4CH mismatch?

Confirm all channels toggle at the module connector and compare the host’s channel mode/mapping/timing to the module’s interface definition.

Can a bridge/scaler convert a non-4CH output into 4CH LVDS reliably?

Sometimes, but it adds complexity and failure points; validate timing, latency, EMI, and lifecycle support carefully.

When is customization preferable for 4CH LVDS projects?

When harness constraints, unusual timings, or long lifecycle requirements make standard options risky, customizing the integration can reduce field issues.

Conclusion

4CH LVDS is a four-channel parallel LVDS transport used to deliver higher pixel throughput with better per-channel margin. It is a hard interface requirement—not redundancy—so success depends on host capability, correct mapping, synchronized harness design, and locked timing definitions. Because “which resolutions use it” depends on the full timing and environment margin, treat resolution as a hint and confirm the required channel definition in the module’s documentation, then validate the complete signal chain under real conditions.

At LCD Module Pro, we support high-bandwidth LCD display module integrations by focusing on interface definition clarity, harness-aware validation, and lifecycle change control so 4CH LVDS systems remain stable from prototype through production.

✉️ info@lcdmodulepro.com

🌐 https://lcdmodulepro.com/

-

Understanding 4CH LVDS is crucial for ensuring reliable integration in LCD modules, enhancing performance and reducing issues. ↩

-

Exploring TCON will enhance your knowledge of display systems and their operational requirements. ↩

-

Understanding intermittent artifacts can help you troubleshoot and improve your electronic systems effectively. ↩

-

Exploring this link will provide insights into how higher pixel throughput enhances display performance in various applications. ↩

-

Understanding synchronized LVDS channels is crucial for ensuring proper data transmission and integrity in your designs. ↩