During product development, one of the most common LCD display module bring-up issues is a “shifted image.” You send a test pattern to the module, but the content appears consistently moved to the left, right, up, or down. This can be frustrating, but it is also a highly diagnostic symptom because it is usually deterministic and repeatable.

A stable shifted image on an LCD display module typically indicates a timing boundary interpretation mismatch—most commonly caused by incorrect polarity or edge-reference settings for synchronization signals such as HSYNC, VSYNC, or related data-capture timing. The fastest path to resolution is to distinguish polarity/edge problems from porch or pixel-count timing errors, then confirm the correct configuration with test patterns and instrumented verification at the module input.

In LCD display module integration work, a shifted image is often better news than flickering, sparkles, or a blank screen. A stable offset usually means the pixel data path is fundamentally working, while the module is starting the active image at the wrong line or pixel position. In other words, the module and the host controller disagree about when a new line or a new frame begins, and that disagreement tends to come from a polarity or sampling-edge mismatch rather than a random hardware failure.

In practical terms, the module’s timing controller (TCON)1 may expect a particular “active” level or edge to mark the start of a line or frame, while the host is driving or configured for the opposite. The result is a predictable, repeatable offset—often a fixed number of pixels or lines—across resets and power cycles. The key to quick debugging is to treat the symptom as a configuration mismatch first, then validate it with objective measurements.

What does an “image shifted” symptom usually indicate?

A shifted image is a specific artifact that points toward a synchronization boundary problem rather than a pure signal quality problem. This distinction is important because it changes the debugging strategy from “hunt noise” to “verify timing interpretation.”

A consistently shifted image indicates a mismatch in how the host controller and the LCD display module interpret the timing boundaries for lines and frames. The module receives valid pixel data but latches it using an incorrect reference point, causing the entire active image area to appear at a stable, fixed offset.

When troubleshooting, it helps to confirm the symptom signature up front:

- Stability: The shift is constant and repeatable across power cycles. It does not flicker or drift randomly.

- Offset: The entire image is displaced, often leaving a black bar or garbage-filled area on one side (sometimes two sides).

- Intact geometry2: Content is largely correct—no obvious stretching, rolling, or random pixel errors (“sparkles”).

This signature is different from other common LCD module issues. Signal integrity problems typically show up as intermittent pixel noise or flicker. Incorrect pixel counts or blanking values often lead to wrapping/rolling, clipping, or distorted geometry. A stable shift, however, strongly suggests the “zero point” (where active video begins) is being recognized at the wrong level or edge.

Which polarity signals can cause a shifted image, and why?

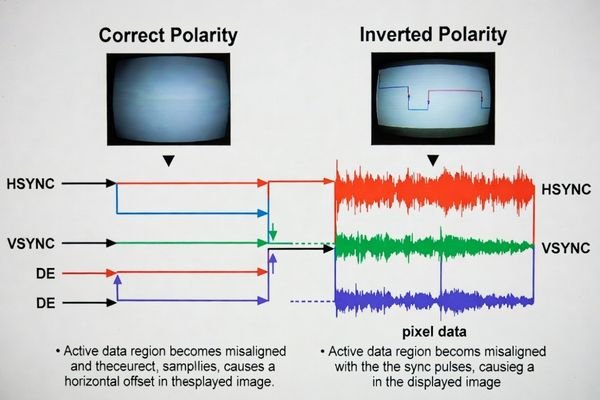

Several key timing relationships in common LCD module interfaces can cause a shifted image if their polarity or active-edge assumptions are misconfigured. These signals define the timing scaffold the module uses to place pixels and lines correctly.

Polarity and edge-reference settings for HSYNC (horizontal sync), VSYNC (vertical sync), and DE (data enable), along with pixel data sampling relative to the pixel clock, are common drivers of a shifted image. If the module recognizes line or frame boundaries on a different active level/edge than the host provides, it will start counting from the wrong moment, creating a stable offset.

In many projects, the root cause is a mismatch between the host controller configuration and the module’s documented timing requirements. The following areas are the most common places to check:

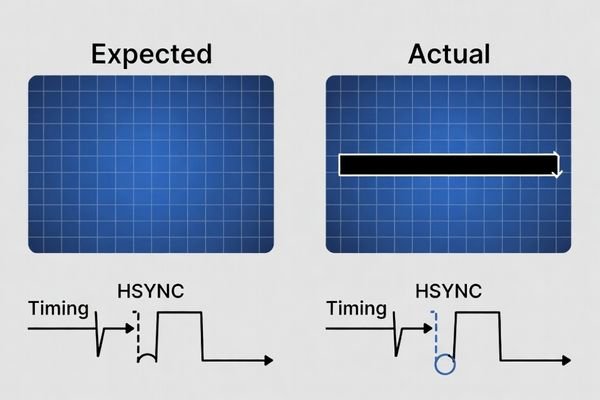

HSYNC and VSYNC polarity

HSYNC indicates when a new line begins, and VSYNC indicates when a new frame begins. These signals are typically defined as active-high or active-low, and the module may treat a specific edge (rising or falling) as the boundary reference. If the host is configured for an active-low HSYNC pulse but the module expects active-high (or expects the opposite edge), the module can lock onto the wrong boundary. The result is that every line or frame begins “late” or “early” by a fixed amount, producing a stable horizontal or vertical shift.

Data enable (DE) polarity3

In interfaces that use DE, it marks when pixel data is valid for the active display region. If DE polarity is inverted, the module may treat blanking intervals as active data time, and treat active video as invalid. Depending on the controller and panel behavior, this can present as a strong displacement, unexpected blank bars, or an active area that appears in the wrong position.

Pixel clock edge relationship

The pixel clock (PCLK) defines when the module samples pixel data. Some modules sample data on the rising edge, while others sample on the falling edge. If the host and module disagree, the symptom can range from a subtle one-pixel-to-several-pixel misalignment (especially visible on sharp vertical edges) to more pronounced boundary-related artifacts. Because clock/data setup and hold margins vary by design, this issue can also appear “almost correct” at room temperature and become unstable at temperature extremes, making it important to validate margins as well as the nominal setting.

How do you isolate polarity issues from porch and resolution timing errors?

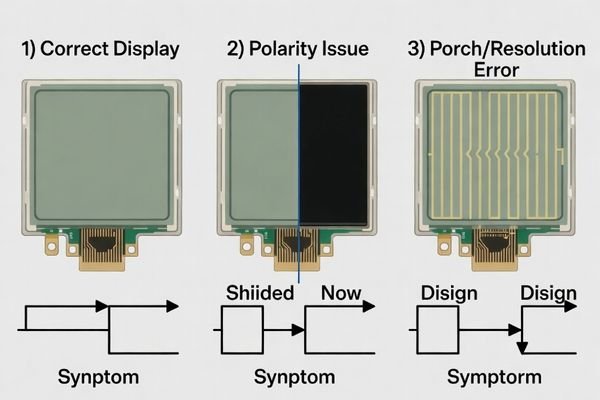

A shifted image can also be caused by incorrect timing parameters, such as active resolution counts or porch/blanking intervals. The goal is to determine whether you have a “where to start” problem (boundary recognition) or a “how big is the canvas” problem (total timing).

Isolate polarity and edge-reference issues by checking whether the image geometry is correct but simply displaced. If the picture is stretched, clipped, wrapped, or rolled, the issue is more likely incorrect active pixel counts or porch/blanking values rather than a pure polarity mismatch. A full-screen border pattern is one of the fastest ways to make this distinction visible.

A simple diagnostic test is to display a static pattern consisting of a thin, one-pixel-wide border around the full active area, optionally with a marker line near the left edge:

- If you see a stable shift: The border is complete and intact, but it is displaced from the physical edges. For example, the left border appears a fixed number of pixels from the left edge while a black bar appears on the right. This strongly suggests polarity/edge-reference4 or sampling relationship issues.

- If you see clipping or wrapping: The border is missing or duplicated on one or more sides, or the image appears to wrap around. This indicates the host’s total pixels per line or total lines per frame do not match what the module expects, pointing to active counts or porch/blanking parameters.

This test quickly separates deterministic boundary interpretation problems from incorrect total timing configuration.

What step-by-step checks confirm the correct polarity configuration?

Once polarity or edge-reference mismatch is suspected, a systematic approach is the fastest way to converge on the correct configuration. The objective is to confirm which level/edge the module uses to define line/frame boundaries and when it samples pixel data—then prove the relationship at the module input.

To confirm the correct polarity and edge settings, first review the LCD display module timing documentation and align the host controller’s HSYNC, VSYNC, DE, and sampling-edge configuration. Then probe the signals at the module input to verify the polarity and the boundary-to-data relationship matches the documented requirements.

Here is a step-by-step process that keeps the work objective and repeatable:

- Read the timing requirements: Identify the required active level/edge for HSYNC, VSYNC, and DE (if used), and the sampling edge relationship for pixel data. Pay attention to any notes about boundary recognition (edge vs level), not just “active-high/low.”

- Check host controller configuration: Compare the controller polarity bits and clock sampling settings against the module requirements. If your platform supports it, make these settings runtime-switchable for faster iteration.

- Use a deterministic test pattern: Use a border or grid pattern, plus a near-edge marker. This makes small offsets visible and makes “geometry correct vs incorrect” obvious.

- Instrument at the right place: Probe HSYNC, VSYNC, PCLK, DE (if present), and one or two data lines as close to the module input connector as possible, not only at the controller output.

- Verify boundary-to-data alignment5: Trigger on VSYNC, then inspect HSYNC and the first active pixels of a line. Confirm that the module’s expected boundary (level/edge) corresponds to the start of valid active pixels, and that data is stable around the sampling edge.

- Check the full signal chain: If you have any intermediate devices (level shifting, timing conversion, serializer/deserializer), verify they are not inverting polarities or shifting edges. Confirm the waveform at the module input matches what the module expects.

- Lock the result with robustness checks: After the shift is corrected, validate under realistic conditions—different test patterns, frame rates within the allowed range, and long-duration operation—to ensure the configuration is stable and not dependent on fragile margins.

This turns a guessing exercise into a controlled engineering verification flow.

How do you choose an LCD display module that reduces integration risk for polarity and timing issues?

Polarity-related issues are typically fixable in configuration, but module selection can significantly reduce bring-up effort by minimizing unnecessary complexity and reducing opportunities for boundary inversion or misinterpretation. The goal is to keep the signal chain simple and the timing requirements unambiguous.

To reduce integration risk, select an LCD display module with an interface that aligns closely with your host controller’s native output and a datasheet that explicitly defines timing boundaries, polarities, and sampling relationships. Minimize additional conversion stages that can invert or reshape timing signals, and prioritize suppliers that can support bring-up with clear documentation and responsive engineering guidance.

At MEIDAYINGNUO, we advise customers to de-risk integration by evaluating the entire chain:

- Native interface alignment: Prefer a module interface that matches the host output to reduce converters or bridges that can invert polarity or introduce skew.

- Clear timing documentation: Look for explicit timing tables and diagrams that define polarities, boundary recognition, and sampling relationships. Ambiguity here directly translates into bring-up time.

- Reasonable timing margins: Favor solutions with adequate setup/hold margin relative to the host controller’s capabilities so the design is stable across temperature, voltage, and process variation.

- Validation access: Ensure your PCB design allows probing key timing and data lines at the module input, so issues can be confirmed quickly without guesswork.

- Lifecycle stability: Choose a module with stable supply continuity and clear change control so a validated timing configuration remains valid across production batches.

FAQ

If changing polarity fixes the shift, does that mean my porch timings are correct?

Not necessarily, but it is a strong sign the module was recognizing boundaries on the wrong level or edge. After the shift disappears, verify the active area starts and ends where expected using a border pattern, and confirm there is no subtle clipping at the edges.

Why is the image shifted but stable instead of rolling or flickering?

A stable shift usually means the module is consistently latching data with a consistent—but wrong—reference point. Rolling and flicker are more typical of missing synchronization, unstable clocks, or marginal signal integrity.

Can a level shifter or bridge device invert polarity without me noticing?

Yes. Intermediate devices and board-level circuits can invert or reshape timing signals, and default configurations may differ from your expectations. That is why measuring both at the controller output and at the module input is important.

How do I test polarity quickly without rewriting a lot of firmware?

Use a minimal bring-up mode where you can flip timing polarity bits and sampling edges at runtime, and display a simple deterministic pattern (border + markers). Faster iteration helps you converge on the correct combination quickly.

Could power or backlight issues look like a polarity-caused shift?

Power issues more often cause flicker, dimming, resets, or random artifacts, but severe noise can make timing edges ambiguous in borderline designs. If the offset changes with backlight level or load, evaluate power integrity, grounding, and margin.

What evidence should I capture to share with the module supplier for faster support?

Capture photos of test patterns, the host timing configuration (registers or configuration files), and measurements at the module input showing the relationship between line/frame boundaries and the first active pixels. This makes it easier to distinguish polarity/edge mismatch from blanking or sampling issues.

If the display is correct at room temperature but shifts in cold or hot conditions, is it still polarity?

Pure polarity misconfiguration is usually temperature-invariant. Temperature-sensitive offsets more often indicate margin issues—clock jitter, signal integrity, or power stability—so validate with measurements under temperature and assess robustness.

Conclusion

A stable, shifted image on an LCD display module is a classic symptom of a timing boundary interpretation mismatch, most commonly related to incorrect signal polarity or sampling-edge configuration. The key to a fast resolution is to treat it as a configuration and verification problem—not a random hardware failure. Use deterministic test patterns to distinguish polarity/edge problems from porch or pixel-count timing errors, then verify the boundary-to-data relationship at the module input with an oscilloscope or logic analyzer.

At MEIDAYINGNUO, our engineering approach focuses on helping customers resolve common bring-up challenges with clear timing documentation and responsive technical support. By selecting a module with well-defined interface timing and minimizing unnecessary signal-chain complexity, you can turn a frustrating “shifted image” issue into a repeatable, satisfying fix.

✉️ info@lcdmodulepro.com

🌐 https://lcdmodulepro.com/

-

Understanding TCON is crucial for diagnosing display issues, as it plays a key role in image stability and synchronization. ↩

-

Exploring intact geometry can provide insights into maintaining image quality and preventing distortion. ↩

-

Exploring DE polarity can help you grasp its impact on display quality, ensuring accurate pixel data representation. ↩

-

Exploring these concepts will deepen your knowledge of display calibration and troubleshooting. ↩

-

Exploring boundary-to-data alignment techniques can enhance your signal processing accuracy and reliability. ↩