During system integration, one of the most common display issues engineers face is a cropped image on an LCD display module. Parts of the user interface may be missing from one or more edges, even though the panel powers on normally and the visible image appears stable. This symptom can delay bring-up because it looks simple at first, but the root cause may sit in different layers of the display signal chain.

A cropped image on an LCD display module is usually caused by a mismatch between the host output and the panel’s native requirements. In most integration cases, the issue comes from incorrect resolution mapping, timing parameters, scaling behavior, or signal-chain configuration rather than from a physical panel defect.

Based on my LCD display module integration work at LCD Module Pro, I have seen this problem repeatedly in embedded and industrial projects. The most common mistake is to start changing timing values1 randomly before documenting the cropping pattern. That approach wastes time and often introduces new variables.

A better diagnosis starts with structured observation. Engineers should first confirm which edges are affected, whether the image geometry remains stable, and whether the display content is clipped, scaled, or shifted. Once that baseline is established, the comparison between the actual host output and the panel datasheet becomes much more efficient. A cropped LCD image is usually a configuration problem, and it should be isolated methodically.

What Does a Cropped Image Usually Indicate in an LCD Display Module?

A cropped image usually means the active image area being generated by the system does not align with the panel’s expected display window.

In most LCD module integrations, a cropped image indicates that the active pixel area, timing definition, or image mapping does not match the panel’s native specifications. The symptom is usually a stable but incomplete image rather than a sign of panel hardware failure.

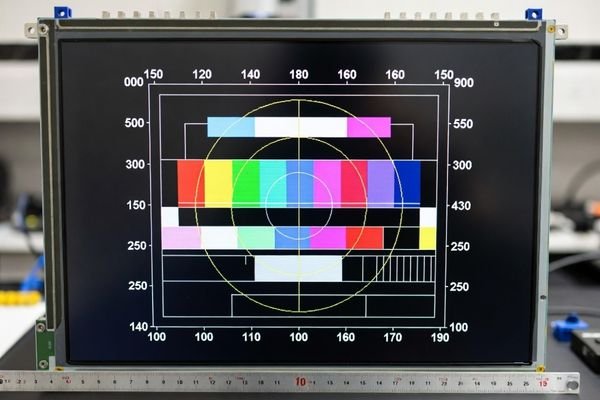

When I begin diagnosing this issue, I first ask for a full-screen test pattern with borders, corner markers, and simple reference shapes. That immediately makes the fault visible in a way that screenshots or verbal descriptions often do not.

Characterizing the Cropping Pattern

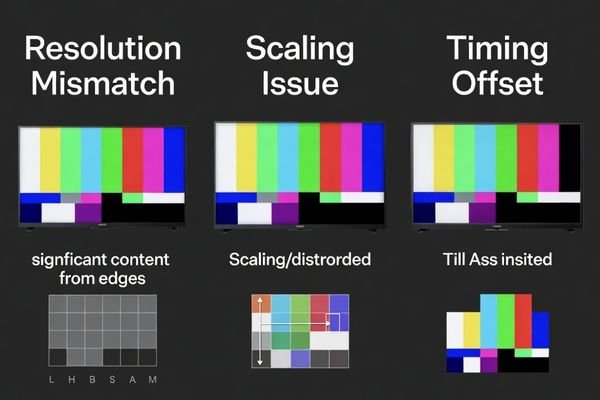

The first diagnostic step is to define exactly how the image is being cut off. Is the cropping limited to one side, such as the right edge only? Does it affect two edges, such as the right and bottom? Is the visible content correctly proportioned, or does it appear stretched or scaled? These observations help distinguish timing offset from scaling or resolution mismatch.

Differentiating Configuration Issues from Hardware Faults

A stable cropped image is usually a configuration issue2, not a physical panel defect. A defective panel is more likely to show lines, dead areas, flicker, or total image failure. Cropping is a data-mapping problem, which means engineers should focus first on resolution settings, timing parameters, display controller configuration, scaler behavior, and initialization tables rather than assuming the LCD module itself is damaged.

Where Do Resolution and Timing Mismatches Usually Come From?

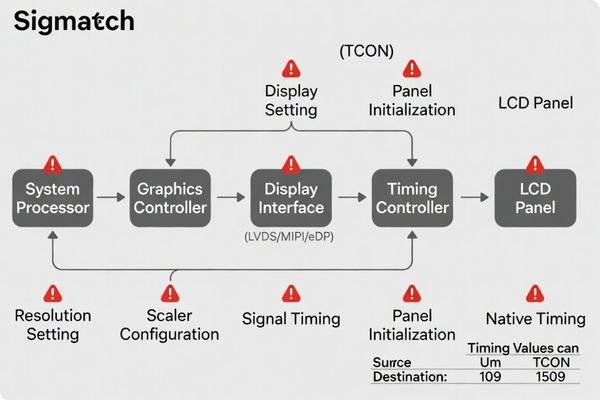

Resolution and timing mismatches usually originate in the display signal chain, where one stage generates output that the next stage does not interpret in exactly the way the panel expects.

In most integration projects, cropped LCD images are caused by incorrect display controller settings, panel initialization code, scaler configuration, or driver board firmware. The root cause is often an incorrect implementation of the timing table defined in the panel datasheet.

From an engineering standpoint, I trace the issue from the source output toward the panel. The key question is where the expected pixel matrix3 starts to diverge from the actual transmitted signal. A mismatch may begin at the host SoC, at an intermediate scaler or driver board, or inside the panel initialization sequence.

A common example is when the host processor outputs a standard video timing such as 1920×1080 at 60 Hz, but the LCD module expects a panel-native timing profile with different porch values, total pixel counts, or sync definitions. The active resolution may look correct on paper, yet the visible image can still shift or crop because the full timing structure is wrong.

Another frequent source is the panel initialization script, especially in MIPI-DSI designs. If the panel commands are incomplete or incorrect, the internal timing controller may not define the active image area properly. In systems using an external driver board, the firmware may apply a preset timing profile that overrides the host configuration and creates a mismatch before the signal ever reaches the LCD module.

How Can You Tell Whether the Cropping Issue Is Caused by Resolution, Scaling, or Timing?

The fastest way to diagnose a cropped image is to separate three related but different causes: incorrect resolution, incorrect scaling, and incorrect timing.

You can usually differentiate the cause by observing how the visible image behaves. Incorrect resolution truncates the image area, incorrect scaling resizes or overscans the full image, and incorrect timing shifts or trims the active image while the visible content remains geometrically stable.

When I troubleshoot this issue, I use a test pattern with a circle, border, and grid because it makes distortion and clipping easier to distinguish. A stable but offset image points in a different direction than a proportionally resized image.

| Potential Cause | Visual Symptom | Likely Root Cause |

|---|---|---|

| Incorrect Resolution | A large portion of the image is missing, as if the panel is showing only part of a larger desktop or frame. | The host is outputting a resolution that does not match the panel’s native pixel matrix. |

| Incorrect Scaling4 | The entire image is visible but stretched, squashed, underscanned, or overscanned symmetrically. | A scaler in the host SoC or an external driver board is enabled and misconfigured. |

| Incorrect Timing | The image has the correct apparent resolution and aspect ratio, but it is shifted, with one or more edges cut off and black bars on the opposite side. | The active resolution is correct, but porch values, sync widths, total timing, or clock settings are wrong. |

These visual differences are the key to efficient diagnosis. If the visible image keeps the correct geometry but is shifted or clipped at one edge, the issue is more likely timing-related than resolution-related. If the whole image is present but resized incorrectly, scaling should be checked before changing panel timing values.

Which Technical Checks Matter Most When Diagnosing Cropped LCD Images?

The most important checks are the panel’s native resolution, the full timing table in the datasheet, and the actual display configuration being generated by the system.

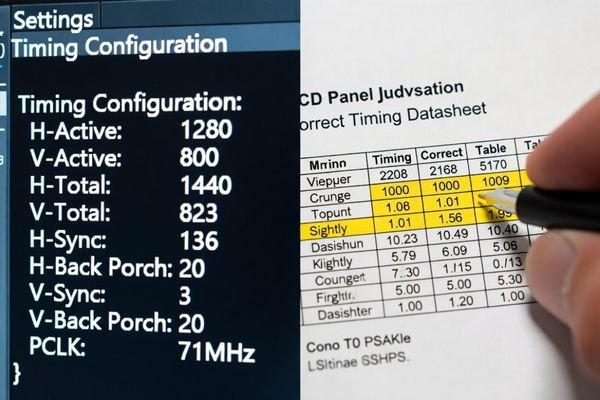

The most critical technical checks are the active H/V pixel counts, total H/V pixel counts, porch values, sync pulse widths, sync polarity, and pixel clock defined in the host configuration compared against the panel datasheet timing table. Resolution alone is not enough if the full timing structure is wrong.

Based on the projects I support, cropped-image problems are often caused by timing values that are close to correct but not exact. That is why engineers should compare the implemented configuration line by line against the panel reference rather than assuming the issue is minor.

Validating the Entire Timing Definition

Resolution describes only the active display area. The complete timing definition also includes the blanking intervals and synchronization structure that position the image correctly within each line and frame. Engineers should verify every key parameter:

- H-Active / V-Active: The visible pixel area.

- H-Total / V-Total: The full number of clocks per line and lines per frame.

- Front Porch / Back Porch / Sync Width: The blanking structure that positions the active image window.

- Pixel Clock (PCLK)5: The transmission rate for pixel data.

- Sync Polarity: Where required by the panel or signal path.

A mismatch in any of these values can produce an image that looks stable but is cropped, offset, or incompletely mapped.

Auditing the Full Signal Path

It is also necessary to confirm that the intended timing values are preserved through the entire signal path. In an embedded design, this may include the device tree, display controller registers, BSP configuration, scaler settings, FPGA timing blocks, or driver board firmware. A common mistake is to correct the timing in the host but leave an external board or intermediate processor configured with a conflicting preset. The panel datasheet timing table should remain the baseline reference throughout diagnosis.

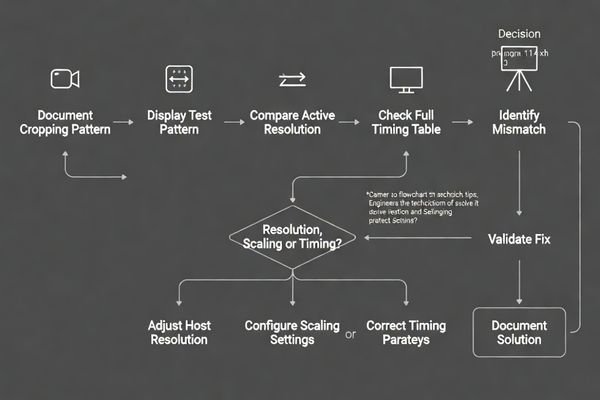

What Is the Most Reliable Workflow for Fixing a Cropped LCD Display Module Image?

The most reliable workflow is one that documents the symptom clearly, checks the full timing definition against the panel reference, and changes only one variable at a time.

A disciplined repair workflow starts by documenting the cropping pattern with a test image, then comparing the host’s full timing configuration with the panel datasheet. After that, engineers should adjust one suspect parameter at a time and validate each change under repeated operating conditions.

In practical debugging, I recommend moving from observation to comparison, then to controlled correction and final validation. This prevents unnecessary changes and makes the result easier to reproduce across sample units.

Documentation and Baseline Analysis

Before changing anything, display a test pattern with clear borders and corner markers and record exactly which edges are missing and by how much. Then compare the panel datasheet against the current display configuration side by side. Create a small timing table for the required and implemented values, including PCLK, H/V Active, H/V Total, porches, and sync widths. This baseline often reveals the most likely mismatch before any code is changed.

Incremental Correction and Validation

Do not modify multiple timing values at once. If the image is shifted horizontally, start with the horizontal timing structure6. If the visible area is vertically cut off, review the vertical timing first. Make one measured adjustment, reboot or reload the display path, and observe whether the image moves in the expected direction. Once the image fills the LCD module correctly, validate the fix across cold boots, repeated power cycles, and different content sources to make sure the timing remains stable under normal operating conditions.

FAQ

What is the first thing to check when an LCD module image is cropped?

The first thing to check is whether the host output resolution matches the panel’s native resolution and whether the missing image area is consistent on one edge, multiple edges, or all content types.

Can correct resolution still produce a cropped image?

Yes. Even if the resolution is correct, incorrect timing values such as sync width, back porch, front porch, or pixel clock can still cause the visible image area to shift or be cut off.

Is cropped display always caused by the LCD panel itself?

No. In most cases, cropping is caused by configuration mismatch in the host output, timing generator, scaler, driver board, or initialization settings rather than by a physical panel defect.

How can engineers tell the difference between scaling and timing problems?

Scaling problems usually resize the full image disproportionately or apply overscan-like behavior, while timing problems more often shift, trim, or misplace the active image area despite otherwise stable image geometry.

Why is a test pattern important for cropped image diagnosis?

A test pattern with clear borders, corner markers, and reference shapes makes it easier to identify exactly which part of the active area is missing and whether the issue is caused by offset, scaling, or incorrect timing.

What should be validated after adjusting timing settings?

Engineers should validate the fix using multiple test patterns, repeated boot tests, and different content sources to confirm the image fills the LCD module correctly under all normal operating conditions.

Conclusion

Diagnosing a cropped image on an LCD display module requires a structured engineering process rather than random parameter changes. In most cases, the issue is caused by mismatch in resolution mapping, timing definition, scaling behavior, or intermediate signal-chain configuration rather than by a failure in the panel itself. The most effective approach is to document the cropping pattern, compare the full host timing definition against the panel datasheet, and verify where the active image area stops matching the LCD module’s native requirements.

At LCD Module Pro, I recommend treating cropped-image diagnosis as a signal-chain configuration task. When engineers work from a known test pattern, use the panel datasheet as the baseline reference, and validate each timing change carefully, they solve integration problems faster and reduce bring-up risk. A correctly configured LCD module is a stable and dependable LCD module, and disciplined timing alignment is a key part of achieving that result.

✉️ info@lcdmodulepro.com

🌐 https://lcdmodulepro.com/

-

Understanding the best practices for timing values can help prevent common mistakes and improve integration efficiency. ↩

-

Identifying configuration issues can save time and resources, leading to quicker resolutions of display problems. ↩

-

Understanding pixel matrix is crucial for diagnosing display issues and ensuring optimal image quality. ↩

-

Exploring the effects of incorrect scaling will enhance your troubleshooting skills for image display problems. ↩

-

Understanding Pixel Clock (PCLK) is crucial for optimizing display performance and ensuring accurate image rendering. ↩

-

Adjusting horizontal timing structure can resolve image shifting issues, making it essential for display optimization. ↩